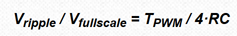

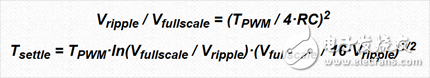

Each PWM DAC design requires analog filtering to separate the required DC component (proportional to the PWM duty cycle) from the unwanted AC ripple. The simplest method is to use a basic RC low-pass filter that gives peak-to-peak ripple amplitude (this is the worst case for a 50% PWM duty cycle, where TPWM = PWM cycle time, and assuming RC TPWM) :

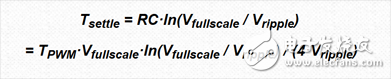

The obvious design trade-off is that although selecting a sufficiently large RC product can achieve any desired ripple attenuation, the settling time will be affected accordingly. For example, if we (rather logically) choose the definition of the stability band equal to the ripple amplitude, then:

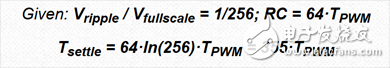

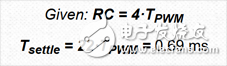

The result of this relationship can be illustrated by an 8-bit example:

Here, even with a fairly fast 32kHz (31μs TPWM), the settling time is still a rather verbose 11ms.

Obviously, if the settling time is a key design parameter, we need to do better and find a filtering solution that will not be too simple. One of the design examples I wrote earlier, "Fast stable synchronous PWM-DAC filter has almost no ripple" illustrates the great possibility along this line of thought.

But not every application can't tolerate lengthy 355TPWM settling time or it can prove really need such a complicated filtering scheme. This design example addresses these common application problems. As shown in Figure 1, it enhances the basic R1/C1 low-pass filter with an inverter, R2, and C2; the inverter, R2, and C2, together, subtract and subtract from the desired DC signal. (Most of the) unneeded AC components, resulting in a relatively clean analog signal output, and its settling time is much shorter than a simple RC filter.

Figure 1: Waveforms and schematics of the PWM DAC Ripple Canceller.

However, how clean is "relatively clean"? How fast is "faster"? With R2=R1 and C2=C1, the ripple and settling time for the new circuit are:

Again refer to the 8-bit example (see Figure 1):

With a cycle of 32 kHz, the speed is increased by 16 times and the ripple-amplitude ratio is doubled!

For many applications, this is a very valuable compromise between a modest increase in circuit complexity and a significant increase in the performance of the PWM DAC.

Networking Keystone Jacks, Punch Down Type Terminals.China Network & Accessories,Networking KEYSTONE Jacks supplier & manufacturer, offer low price, high quality Punch Down Type Terminals,, etc.

Networking KEYSTONE Jacks, Punch Down Type Terminals.China Network & Accessories,Networking KEYSTONE Jacks supplier & manufacturer, offer low price, high quality Punch Down Type Terminals,, etc.

Networking KEYSTONE Jacks, Punch Down Type Terminals.China Network & Accessories,Networking KEYSTONE Jacks supplier & manufacturer, offer low price, high quality Punch Down Type Terminals,, etc.

Network & Accessories,Networking KEYSTONE Jacks, Punch Down Type Terminals

ShenZhen Antenk Electronics Co,Ltd , https://www.atkconnectors.com