introduction

The EP7209 is the world's first digital audio decoder system-on-a-chip that supports both the popular MP3 standard and the fast-growing Internet audio compression standard such as Microsoft Audio. The EP7209 operates at 74MHz with the same performance as a 100MHz Intel Pentium-based PC and consumes very little power: at 2.5V, it consumes less than 170mW. Its arm core provides the processing power that an excellent digital signal processor can provide, so Internet audio processing takes up only 50% of the chip's processing power. This leaves the embedded system designer with up to 25 MIPS (millions of instructions per second) of processing power for other functions. This article focuses on the structure, function, interface characteristics of EP7209 and its application in embedded systems.

First, the functional block diagram and function block description

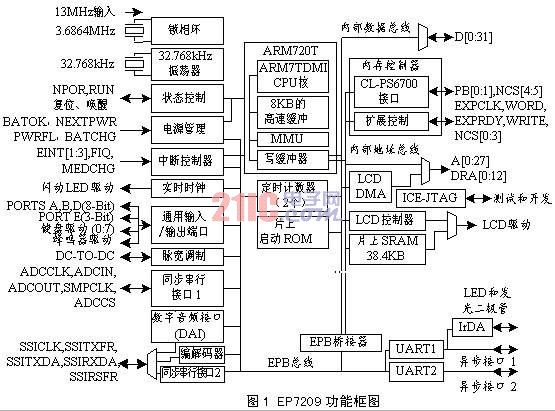

Figure 1 is a functional block diagram of the EP7209. It can be seen from Fig. 1 that EP7209 contains the following functional blocks.

(1) The arm720T processor contains the following functional sub-blocks:

1arm7TDMI CPU core. The CPU core supports the Thumb instruction set, core debugging, enhanced multipliers, JTAG, and embedded ICE. Its clock rate is programmable to 18MHz, 36MHz, 49MHz, and 74MHz.

2 The Memory Management Unit (MMU) is compatible with the arm710 core and adds support for Windows CE. The memory management unit provides address translation and a conversion bypass buffer with 64 entries.

3 provides 8KB of single instruction and data cache and a four-way associative cache controller.

4 write buffer.

(2) 38400 bytes of on-chip SRAM that can be shared between the LCD controller and the general purpose application.

(3) The memory can be interfaced with up to 6 independent extension segments, each of which has 256MB and the wait state is programmable.

(4) 27-bit general purpose I/O that can be multiplexed to provide additional functionality when needed.

(5) The Digital Audio Interface (DAI) can be directly connected to a CD-quality DAC and codec.

(6) Interrupt controller.

(7) Advanced system state control and power management.

(8) Two 16550A compatible full-duplex UARTs with 16-byte transmit and receive FIFOs.

(9) SIR protocol infrared data codec with a maximum rate of 115.2 kbps.

(10) LCD controller, 16-level gray scale, programmable to 1, 2 or 4 bits per pixel.

(11) On-chip boot ROM, the boot code for serial loading has been solidified.

(12) Two 16-bit general-purpose timer counters.

(13) A 32-bit real-time clock (RTC) and comparator.

(14) Two synchronous serial interfaces for Microwire or SPI peripheral devices such as ADCs. One interface supports both master and slave modes, and the other only supports master mode.

(15) Full JTAG boundary scan and embedded ICE support.

(16) Two programmable pulse width modulation interfaces.

(17) One interface for connection to one or two Cirrus Logic CL-PS6700 PC Card controller devices to support two PC Card slots.

(18) Oscillator and phase-locked loop for generating 18.432 MHz, 36.864 MHz, 49.152 MHz, or 73.728 MHz clocks required by the external 3.6864 MHz crystal. There is also an external clock input (used in 13MHz mode).

(19) A low-power 32.768 kHz oscillator used to generate the 1 Hz clock required for the real-time clock.

All external memory and peripheral devices should be connected to the 32-bit data bus D[0:31] and should use the 28-bit address bus A[0:27] and other control signals.

This article refers to the address: http://

Second, the basic working principle

The core logic of the EP7209 is built on top of an arm720T embedded processor. The design of the EP7209 is optimized for low power consumption and uses a completely static 0.25μm CMOS fabrication process. The idea of ​​low power consumption is also reflected in the state design and the way the clock is used. The working principle of the EP7209 will be described selectively below.

1. CPU core

The ARM720T consists of an arm7TDMI 32-bit RISC processor, a single cache and a memory management unit (MMU). The 8KB cache has a four-item associated register and is organized into 512 lines of four words (4 x 512 x 4 bytes). The cache is directly connected to the ATM7TDMI, thus caching the virtual address from the CPU. When the required virtual address is not in the cache, the MMU translates the virtual address to a physical address. A 64-item conversion bypass buffer (TLB) is used to speed up the address translation process and reduce the bus transfer required for page table reads. The MMU can save power only by translating addresses that are not stored in the cache.

2. State control

The EP7209 supports the following power management states: Operation, Idle, and Backup (Energy Saving), as shown in Figure 2. The normal program execution state is the operating state. This is a full performance state with both clock and peripherals enabled. The idle state is the same as the operating state except that the CPU clock is suspended. An interrupt or wake-up will return the idle state to the operational state. The power consumption is minimized in the standby state. Selecting this mode turns off the main oscillator and supplies power only to the real-time clock and associated logic. When the EP7209 is in the standby state, it is important to keep all power and ground pins connected to the power supply and ground in order to ensure that the system wakes up normally. The only state in which the backup state can be changed is the operational state.

3. Reset

The EP7209 has three asynchronous reset signals: nPOR, nPWRFL, and nURESET. As any of them is active, a system reset will be generated internally. All EP7209 internal registers will be reset except for the RTC data and match registers. In order for the system time to be maintained in the event of a user reset or power failure, the RTC data and match registers are only cleared by a reset caused by nPOR.

Any reset will reset the CPU and cause the CPU to execute the program from the reset vector when the EP7209 returns to the operating state.

4. Clock

The EP7209 has two clock modes: an external clock input and an on-chip PLL. The clock source is selected by a trap option on pin 2 (PE) of port E. If the PE is high at the rising edge of nPOR (eg, at power-up), the external clock mode is selected; if PE is low, then the on-chip PLL mode is selected. After power-on, PE can be used as a general-purpose input and output port.

The EP7209 device has several independent logic sections, each with its own clock frequency requirement. When the EP7209 is in external clock mode, the actual frequency of the peripheral device will be different from the frequency in PLL mode.

5. Interrupt processing

An exception is usually generated when an unpredictable event (such as an interrupt or memory error) occurs during program execution.

Welcome to the Embedded Learning Network Forum (), interact with 2 million technicians >> Enter

When these exceptions occur at the same time, the order in which they are processed will be determined by the fixed priority service system. Table 1 shows the priority order of all exceptions.

The EP7209 interrupt controller has two interrupt types: Interrupt Request (IRQ) and Fast Interrupt Request (FIQ). The interrupt controller has the ability to control interrupts from 22 different FIQ and IRQ interrupt sources. Of these 22, 17 are mapped to IRQ inputs, while the other 5 are mapped to FIQ inputs. FIQ has a higher priority than IRQ. If two interrupts from the same group (IRQ or FIQ) are received, their service order must be resolved by software. All interrupts are level sensitive, that is, they must be consistent with the following order.

(1) The interrupt device (internal or external) generates an appropriate interrupt.

(2) If the appropriate bit in the interrupt mask register has been set, then an FIQ or IRQ will be generated by the interrupt controller.

(3) If the interrupt is enabled, the processor will jump to the appropriate address.

(4) Interrupt scheduling software reads the interrupt status register to determine the interrupt source and call the corresponding interrupt service routine.

(5) The software in the interrupt service routine will clear the interrupt source by taking some action specific to the device requesting the interrupt (eg, reading the UART RX register).

The interrupt service routine can then re-enable the interrupt. Any other unhandled interrupts will be served in the same way. Alternatively, it can be returned to the interrupt dispatching software. This software can check for any other unprocessed interrupts and schedule them accordingly. Interrupts of the "End of Interrupt" type will be latched. All other interrupt sources (such as external interrupt sources) must remain active until the corresponding service routine begins execution.

6. How to start the EP7209

The 128 bytes of the on-chip boot ROM contain a sequence of instructions. This sequence of instructions initializes the device and then configures UART1 to receive 2048 bytes of serial data. These data are received and placed in the on-chip SRAM. Once the download transfer is complete, execution will jump to the beginning of the on-chip SRAM. This will allow operations such as downloading and programming code into the system Flash during the manufacturing process of the product.

Whether to boot the ROM from the on-chip boot system is determined by the state of the nMEDCHG pin during power-reset. If nMEDCHG is high when nPOR is active, then EP7209 will be booted from the external memory device connected to CS[0] (normal startup mode); if nMEDCHG is low, then the boot will start from the on-chip ROM. Note: In both cases, after the power-on reset is complete, the EP7209 will be in the standby state, and in order to actually begin the boot sequence, there is a low-to-high transition on the WAKEUP pin.

The result of the on-chip ROM boot is that the decoding of all chip selects is flipped. The signal that controls the boot option is latched by nPOR, which means that the remapping of the address and bus width will continue to be applied until nPOR is again valid. After booting from ROM, the contents of the boot ROM can be read back from address 0x0000000; in normal operation, the contents of the boot ROM can be read back from address range 0x70000000.

7. Memory and I/O expansion interface

The EP7209 is capable of decoding six discrete linear memories or extended segments. Two of these can be reserved for PC Cards, each connected to a separate single CL-PS6700 device. Each segment is 256MB in size. Two additional segments (other than these six segments) are used for the on-chip SRAM and the on-chip ROM. The on-chip ROM space is fully decoded and the SRAM space is fully decoded into the maximum size of the video frame buffer (128KB) programmed in the LCDCON register. SRAM space beyond this address range is not fully decoded (ie any access beyond the 128KB range will wrap around to the 128KB range). Either of the six segments can be configured to interface with a conventional SRAM interface, and can be individually programmed to be 8, 16, or 32 bits wide, support page mode access, and can be used for non-contiguous access. Insert 1 to 8 wait states, and insert 0 to 3 wait states when performing trigger mode access. The zero wait state continuous access feature is designed to support the ROM of the trigger mode. For writable memory devices using the nMWE pin, zero wait state continuous access is not allowed, and at least one wait state should be inserted (waiting for the number of states to be programmed into the contiguous field of the appropriate MEMCFG register). The bus cycle can also be extended by using the EXPRDY input signal.

8. Big end configuration and small end configuration

The EP7209 uses a little endian configuration for internal registers. However, it is possible to connect the device to an external memory system configured with a big endian. The big end/small end bits in the arm720T control register set whether the EP7209 is processing in memory in big endian or little endian format. The memory is considered to be a linear combination of bytes numbered starting from 0. Bytes 0~3 hold the first stored word, bytes 4~7 hold the second word, and so on. In the little endian plan, the lowest numbered byte in the word is considered to be the least significant byte of the word, and the highest numbered byte is considered to be the most significant byte of the word. The Byte0 of the storage system should be connected to data lines 7 to 0 (D[7:0]) in this plan. In big endian planning, the most significant byte of the word is stored in the lowest numbered byte, and the lowest byte is stored in the highest numbered byte. Therefore, the Byte0 of the memory system should be connected to the data lines 31 to 24 (D[31:24]). Load and store instructions are the only instructions that are affected by the size and end configuration.

9. LCD controller supporting on-chip frame buffer

The LCD controller provides all the required control signals to interface directly with a single-panel composite LCD. The size of the panel is programmable and can be any width (line length) from 32 to 1024 pixels in 16 pixel increments. The total video frame buffer size is programmable up to 128KB. This is equivalent to the theoretical maximum panel size of 1024 x 256 pixels (4 bits per pixel). The video frame buffer can be located in any memory controlled by the chip select. In any memory controlled by the chip select, its starting address is fixed at address 0X00000000. The starting address of the LCD video frame buffer is defined in the FBADDR[3:0] registers, which become the most important nibble (nibble) of the external address bus. The default starting address is 0XC0000000 (FBADDR=0XC). A system built using on-chip SRAM (OCSR) will use on-chip SRAM for LCD video frame buffering and for storing various data. The LCD video frame buffer start address should be set to 0X6 in this system.

Third, memory mapping

The lower 2GB of the address space is allocated to the memory. In EP7209, the 8KB space just under 2GB is prepared for internal registers and is not accessible. The MMU of the EP7209 should be programmed to generate an interrupt exception when accessing this area.

Internal peripheral components are addressed by a set of internal memory locations from hexadecimal addresses 8000.0000 to 8000.3 FFF. These memory locations are considered internal registers in the EP7209. From 0x8000.0000 to 0x8000.1FFF contain CL-PS7111 compatible registers that are included for backward compatibility and are referred to as old internal registers.

Table 2 shows how the 4GB address space range of the arm720T processor is mapped in the EP7209 (when booting from the on-chip boot ROM will have different memory maps), the memory map shown assumes two CL-PS6700 card controllers Linked up. If this feature is not required, the nCS and nCS memory space is available. The external boot ROM is not fully decoded (ie, the boot code will be repeated in the 256MB byte space from 0x7000.0000 to 0x8000.0000). The SRAM can be fully decoded to the maximum size, 128 KB, and access to any location outside of this range will wrap around this range.

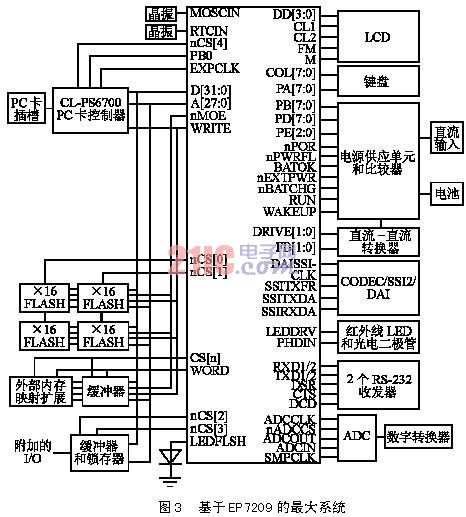

Fourth, the largest system based on EP7209

The maximum configuration system based on EP7209 is shown in Figure 3. This system assumes that the ROM is a 16-bit wide device. The keyboard can be connected to more general purpose input and output port bits than shown in Figure 3 to support more than 64 keys; however, these extra pins will not be pinned to the WAKEUP pin.

It should be noted that the inputs/outputs of the three serial interfaces (DAI, CODEC, and SSI2) are multiplexed with the same set of external interface pins. Therefore, at any one time, the system can only use one of these three peripheral device interfaces.

Conclusion

This paper introduces an ARM7-based audio decoder single-chip system EP7209. Describes the overall structure of the EP7209, how each function block, and the address space of the ARM processor are mapped in EP7209. The basic working principle of EP7209 is explained. Finally, the largest system that can be built based on EP7209 is given. I hope this article will enable developers of embedded systems to understand EP7209 and deepen their understanding of the arm core.

Smart Bms,Bms For Battery,Bms For Lithium Battery,Bms Module

HuiZhou Superpower Technology Co.,Ltd. , https://www.spchargers.com